卷积神经网络

卷积神经网络CNN卷积神经网络的英文全称为Convolutional Neural Network,它是一类强大的、为处理图像数据而设计的神经网络,是一种深度的监督学习下的机器学习模型。基于卷积神经网络架构的模型在计算机视觉领域中已经占主导地位,应用于目标检测、边缘检测、语义分割、图像描述、问答系统、风格迁移等场景。

特征学习阶段图像卷积(卷积层)卷积层是个错误的叫法,因为它所表达的运算其实是互相关运算(cross-correlation)。下面动图很好的展示了图像卷积的过程。首先我们需要有一个卷积核(Kernel或Filter),对于图像上的一个点,让模板的原点和该点重合,然后模板上的点和图像上对应的点相乘,然后各点的积相加,就得到了该点的卷积值。

举例一个处理二维图像数据的例子(暂时不考虑三维)。下面我们输入一个高度是3、宽度是3的二维张量(形象的表达是一个3*3的矩阵)。卷积核的高度和宽度都是2。

输出的卷积层有时被称为特征映射(feature map),因为它可以被视为一个输入映射到下一层的空间维度的转换器。

从[[0,1],[3,4]]开始与卷积核计算。计算完向右移动一个 ...

CNN

神经网络,深度学习,机器学习1.神经网络神经网络,该模型灵感来自动物的中枢神经系统,通常呈现为相互连接的神经元,它可以对输入值通过反馈机制使得它们适应对应的输出。

2.深度学习深度学习是神经网络的进阶版,它的基本思路与神经网络类似,现在所说的深度学习大部分都是指神经网络,但往往比神经网络有着更复杂的结构以及优化算法,是神经网络的纵向延伸,常见的模型有CNN, RNN, LSTM等。

3.机器学习机器学习是一门多领域交叉学科,涉及概率论、统计学、逼近论、凸统计、算法复杂度理论等多门学科。专门研究计算机怎么模拟或实现人类的学习行为,以获取新的知识或技能,重新组已有的知识或技能,重新组织已有的知识结构使之不断改善自身的性能。

机器学习是人工智能的一个分支,也是用来实现人工智能的一个有效手段。简单来说,机器学习就是通过算法,使得机器能从大量历史数据中学习规律,从而对新的样本做智能识别或对未来做预测。使用大量数据和算法来“训练”机器,由此带来机器学习如何完成任务。

机器学习主要分三种形式,监督学习、非监督学习、半监督学习。最常见的是监督学习中的分类问题。监督学习的训练样本都含有“标签”,非监督 ...

形态学图像处理

形态学简介形态学(morphology)是原生物学的专业分支,主要研究的是动植物的形态与结构。在1964年,数学形态学诞生于法国巴黎,1968年成立法国枫丹白露数学形态学研究中心是,它是以形态为基础对图像进行分析的数学工具。90年代至今,数学形态学在模式识别,编码,运动分析,运动景物描述等方面取得进展,用于数值函数的形态学算子开发。

$\textcolor{RubineRed}{具体一点,我们以数学形态学为工具,从图像中提取表达和描绘区域形状的有用的图像分量,如边界、骨架等。}$

集合论形态学的语言是集合论,处理图像时,数学形态学中的集合表示图像中的目标。

元素和集合一幅图像称为一个集合,集合也称样本空间$\Omega $。$\textcolor{BurntOrange}{对于二值图像,可认为取值为1的点对应于图像前景像素,取值为0的点对应于背景。} $

(1)集合元素的运算

集合的基本运算总共有 4 种,分别是交、并、差、补。

a. 交运算

对于集合A、B,交运算(Intersection)被定义为:

b. 并运算

对于集合A、B,并运算(Union)被定义为:

c. 补运算 ...

腐蚀与膨胀

腐蚀形态学公式是根据结构元和前景像素集合A写出的,假设A和B是$Z^2$中的两个集合,B对A的腐蚀(表示为)$A\ominus B$ 定义为

式中,A是前景像素的一个集合,B是一个结构元(SE),z项是前景像素值(1)。

$\textcolor{BrickRed}{这个公式指出,B 对A 的腐蚀是所有点z 的集合,条件是平移z 后的B 包含于A}$(这个位移是相对于B的原点定义的)。

如图所示,我们想用一个SE B去腐蚀Image I,就是要把B完全包含在A的图像中,然后对结构单元进行平移,得到B的中心点的运动轨迹,组成新的图像,此为用B腐蚀A的图像。

图像本身、结构元的形状和原点位置的选取都会影响腐蚀操作的结果。

腐蚀能够消融物体的边界,而具体的腐蚀结果与图像本身和结构元的形状有关:如果物体整体上大于结构元,腐蚀的结构是使物体变“瘦”一圈,这一圈到底有多大是由结构元决定的:如果物体本身小于结构元,则在腐蚀后的图像中物体将完全消失;如物体仅有部分区域小于结构元(如细小的连通),则腐蚀后物体会在细连通处断裂,分离为两部分。因此在实际应用中,可以利用腐蚀运算去除物体之间的粘连, ...

在Vitis中快速创建工程

我发现在2018版本中可以直接生成hdk,并打开,但是在2019.2版本中开始就没有SDK了,生成的文件名后缀是xsa,需要我们单独在Vitis上创建应用工程。

下面我学习了一种简单的将xsa文件添加到vitis中,并创建工程,和大家分享一下。

1.生成.xsa文件:在file中导出Hardware。

2.当程序涉及PL端的应用时,就需要勾选Include bitstream,如果只涉及PS端,就不需勾选。然后点击ok生成 .xsa文件。

3.在Tools中选择Launch Vitis。

4.在打开的Vitis后,选择工程存放文件夹,点击Launch。

5.选择Create Application Project

6.输入Project name,点击next。

7.在第二栏中点击加号选择刚刚生成的.xsa文件,然后next,选择建立Empty Application文件,然后点击Finish。

8.完成工程创建,在src文件夹下建立main.c文件。添加调试程序。

Custom IP

1.Introduction在 Vivado 软件中,通过创建和封装 IP 向导的方式来自定义 IP 核,支持将当前工程、工程中的模块或者指定文件目录封装成 IP 核,当然也可以创建一个带有 AXI4 接口的 IP 核,用于 PS 和 PL 的数据通信。本次实验选择常用的方式,即创建一个带有 AXI 接口的 IP 核,该 IP 核通过 AXI 协议实现 PS 和 PL 的数据通信。AXI 协议是一种高性能、高带宽、低延迟的片内总线,关于该协议的详细内容,可以在我之前的篇节看到。

系统框图

框图中的 UART 用于打印信息,Breath LED IP 核为自定义的 IP 核,PS 通过 AXI 接口为 LED IP 模块发送配置数据,从而来控制 PL LED 灯。 (本实验基于正点原子ZYNQ嵌入式开发指南)

实验任务本章的实验任务是通过自定义一个 LED IP 核,来控制 PL LED 呈现呼吸灯的效果,并且 PS 可以通过AXI 接口来控制呼吸灯的开关和呼吸的频率。

2.Hardware Designstep1.创建一个新的ip核

1-1 打开 Vivado,进入 Vivado ...

AXI GPIO

IntroductionXilinx® LogiCORE™ IP AXI 通用输入/输出 (GPIO) 内核为 AXI 接口提供通用输入/输出接口。 这个 32 位IP内核旨在与 AXI4-Lite 接口连接。(参考Xilinx的开发指南:AXI GPIO v2.0 LogiCORE IP Product Guide(PG144))

Features1* 支持 AXI4-Lite 接口规范

2* 支持可配置的单或双 GPIO 通道

3* 支持 1 至 32 位 GPIO 引脚的可配置通道宽度

4* 支持将每个 GPIO 位动态编程为输入或输出

5* 支持每个通道的单独配置

6* 支持所有寄存器的每一位的独立复位值

7* 支持可选的中断请求生成

注: 具体的配置信息可见 Vivado中 AXI GPIO IP核。

Function DescriptionAXI GPIO 设计为 AXI4-Lite 接口提供通用输入/输出接口。

AXI GPIO 可以配置为单通道或双通道设备。 每个通道的宽度可独立配置。

通过启用或禁用三态缓冲器,端口动态配置为输入 ...

红外图像处理

红外图像处理

1.红外成像和红外热成像的区别

要想知道它们之间的区别,首先要了解两个概念:主动成像和被动成像,

主动成像:主动发射信号然后成像

被动成像不需要发射信号即可成像

(1) 红外热成像(制冷型/非制冷型中长波红外热辐射计)

红外热成像仪的原理是探测目标自身发出的红外辐射,并通过光电转换、信号处理等手段,将目标物体的温度分布图像转换成视频图像,采用应用电子技术和计算机软件与红外线技术的结合,用来检测和测量热辐射。

(2) 红外成像

红外成像一般是主动红外,基本原理是利用截止带宽在短波红外的摄像机可以感受红外光(1um~2um短波红外)的光谱特性,配合配有带通滤波片的灯作为“照明源”来成像;

FIFO

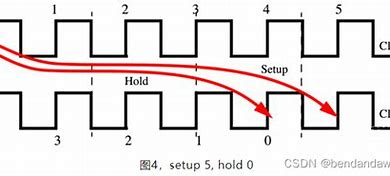

FIFO简介FIFO的英文全称是First In First Out,即先进先出。FPGA使用的FIFO一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存,或者高速异步数据的交互也即所谓的跨时钟域信号传递。它与FPGA内部的RAM和ROM的区别是没有外部读写地址线,采取顺序写入数据,顺序读出数据的方式,使用起来简单方便,其数据地址由内部读写指针自动加1完成,由此带来的缺点就是不能像RAM和ROM那样可以由地址线决定读取或写入某个指定的地址。

同步/异步FIFO1.同步FIFO:指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作。

2.异步FIFO:指读写时钟不一致,读写时钟是互相独立的。

Xilinx 的FIFO IP 核可以被配置为同步FIFO 或异步FIFO,其信号框图如下图所示。从图中可以了解到,当被配置为同步FIFO 时,只使用 wr_clk,所有的输入输出信号都同步于wrclk 信号。而当被配置为异步FIFO 时,写端口和读端口分别有独立的时钟,所有与写相关的信号都是同步于写时钟wr_clk,所有与读相关的信号都是同步于读时钟rdclk ...

DDR

DDR控制原理1. 初识SDRAMSDRAM: (Synchronous Dynamic Random Access Memory),同步动态随机存储器。同步是指其时钟频率与CPU前端总线的系统时钟频率相同,并且内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失:随机是指数据不是线性依次存储,而是自由指定地址进行数据的读写。

物理 Bank:传统内存系统为了保证 CPU 的正常工作,必须一次传输完 CPU 在一个传输周期内所需要的数据。而CPU 在一个传输周期能接受的数据容量就是 CPU 数据总线的位宽,单位是 bit(位)。当时控制内存与 CPU之间数据交换的芯片也因此将内存总线的数据位宽等同于 CPU 数据总线的位宽,而这个位宽就称之为物理 Bank(Physical Bank,Pbank)的位宽。

芯片位宽:每一片SDRAM缓存芯片本身的位宽。但是芯片位宽不等于Pbank,一般芯片位宽会小于Pbank,所以在一台设备中,我们可以用多片SDRAM去匹配Pbank。

2. SDRAM基本结构逻辑 Bank:( Logical Bank,下文简称 ...