At-Speed Patterns and On-Chip Clock Controllers

At-Speed Patterns and On-Chip Clock Controllers

0.Objectives

本次学习的目标是可以为at-speed的ATPG创建patterns

(1)可以完成Transition fault pattern的创建

(2)可以完成path delay pattern的创建

描述一下怎么去定义内部的clock去做atpg的

了解IDDQ的pattern

1.What is the at speed test?

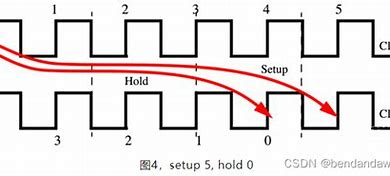

在工艺节点在130nm以下的时候,很多情形下的物理缺陷都是由于延时来引起的。因此在对这种类型的chip做dft的时候,需要建立一个新的故障模型,称之为延时故障模型(time delay model)。解决的方法就是全速测试,所谓的全速测试就是让芯片工作在自己的高频时钟频率上,这个频率往往是要高过ATE*[Automatic Test Equipment 自动测试机台]*时钟的。这样对扫描模型的建立就提出了新的要求。即至少要保证芯片的launch clock和capture clock为芯片内部的高频率时钟。synopsys对此种问题的解决方法就是OCC(on chip clocking)。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Nanchen's Blog!