MMCM/PLL

CMT

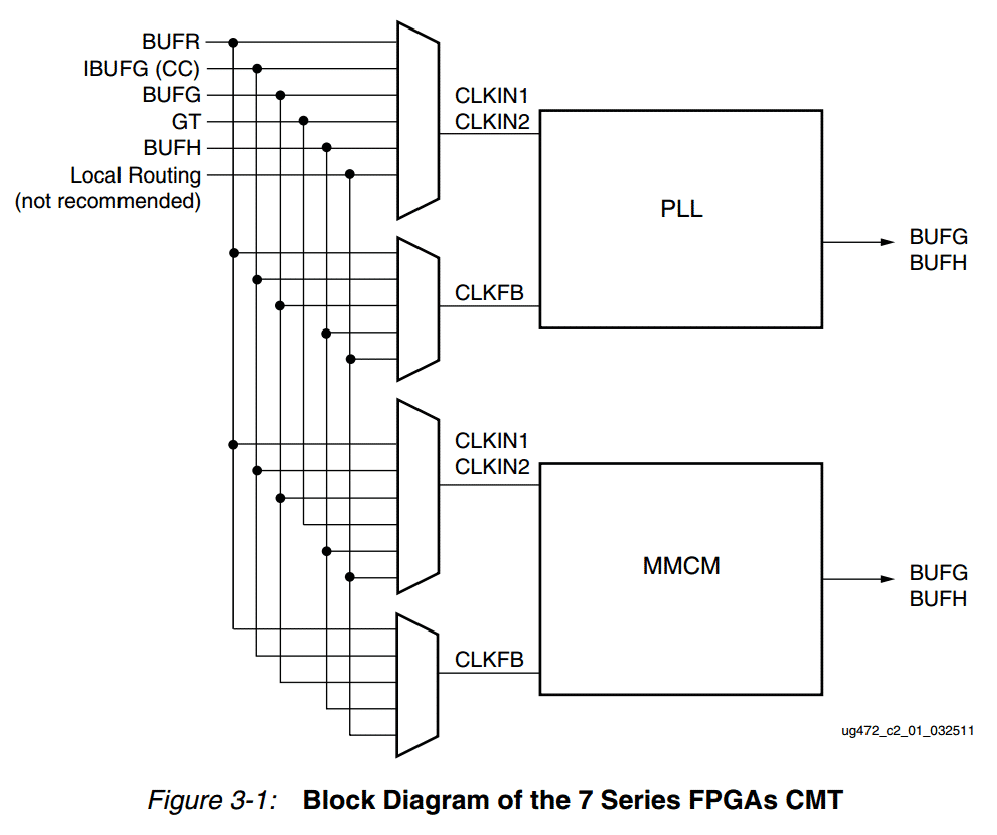

Xilinx 7 系列器件中具有时钟管理单元 CMT 时钟资源,xc7a35t 芯片内部有5 个CMT,xc7a100t 芯片内部有 6 个CMT,为设备提供强大的系统时钟管理以及高速 I/O 通信的能力。Xilinx 7 系列器件中的时钟资源包含了时钟管理单元 CMT,每个CMT 由一个MMCM 和一个PLL 组成。时钟管理单元 CMT 的总体框图如下图所示。

MMCM/PLL 的参考时钟输入:

IBUFG(CC)即具有时钟能力的 IO 输入、区域时钟 BUFR、全局时钟 BUFG、GT 收发器输出时钟、行时钟 BUFH 以及本地布线。

在最多的情况下,MMCM/PLL 的参考时钟输入都是来自IBUFG(CC)即具有时钟能力的 IO 输入,MMCM/PLL 的输出可以驱动全局时钟BUFG 和行时钟BUFH 等等。BUFG 能够驱动整个器件内部的通用逻辑的所有时序单元的时钟端口。

PLL

简介

全称:Phase Locked Loop,即锁相环,是一种反馈控制电路。PLL 对时钟网络进行系统级的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程占空比的功能。

锁相环的特点及应用

锁相环作为一种反馈控制电路,其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位。因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环的来历

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环的组成

PLL 由以下几部分组成:前置分频计数器(D 计数器)、相位频率检测器(PFD,Phase-Frequency Detector)电路、电荷泵(Charge Pump)、环路滤波器(Loop Filter)、压控振荡器(VCO,Voltage Controlled Oscillator)、反馈乘法器计数器(M 计数器)和后置分频计数器(O1-O6 计数器)。

锁相环具体的工作原理

在工作时,PFD 检测其参考频率(FREF)和反馈信号(Feedback)之间的相位差和频率差,控制电荷泵和环路滤波器将相位差转换为控制电压;VCO 根据不同的控制电压产生不同的震荡频率,从而影响Feedback信号的相位和频率。在FREF 和 Feedback 信号具有相同的相位和频率之后,就认为PLL 处于锁相的状态。

在反馈路径中插入M计数器会使VCO的震荡频率是FREF信号频率的M倍,FREF信号等于输入时钟(FIN)除以预缩放计数器(D)。

参考频率用以下方程描述:FREF= FIN/D,VCO 输出频率为 FVCO= FIN×M/D,PLL的输出频率为FOUT=(FIN×M)/(N×O)。

MMCM

MMCM(Mixed-Mode Clock Manager)混合模式时钟管理器,MMCM 功能是PLL 的超集,它是在PLL的基础上加了相位动态调整功能,PLL 是模拟的,而动态调相是数字电路,所以称为混合模式。其相对于PLL 的优势是相位可以动态调整,占用面积较大。MMCM 主要用于驱动器件逻辑(CLB、DSP、RAM 等)的时钟。PLL 是和 IO 资源紧密绑定的,占用面积小,常用于为内存接口生成所需的时钟信号,但也具有与其他器件逻辑的连接,因此如果需要额外的功能,它们可以用作额外的时钟资源。

Xilinx 提供了用于实现时钟功能的 IP 核Clocking Wizard,该IP 核能够根据用户的时钟需求自动配置器件内部的CMT,以实现用户的时钟需求。

Xilinx 官方的手册文档 “PG065,Clocking Wizard v5.2 LogiCORE IP Product Guide”。

硬件设计

本章实验将Clocking Wizard IP 核产生的4 个时钟100MHz、100MHz_180deg 、50MHz、25MHz,连接到 扩展口IO 上。

PLL/MMCM实验中,可以将其理解为:外部时钟连接到具有时钟能力的输入引脚CCIO(Clock-Capable Input),进入MMCM/PLL,产生不同频率和不同相位的时钟信号,然后驱动全局时钟资源BUFG。

具体实验部分参照